### SG1

**Strain Gauge**

**Function Module**

### **MODULE MANUAL**

| REVISION HISTORY                                               | 4  |

|----------------------------------------------------------------|----|

| SG1 DATA SHEET                                                 | 5  |

| INTRODUCTION                                                   | 7  |

| FEATURES                                                       | 7  |

| PRINCIPLE OF OPERATION                                         | 7  |

| Automatic Background Built-in Test (BIT)/Diagnostic Capability | 7  |

| Status and Interrupts                                          | 7  |

| REGISTER DESCRIPTIONS                                          | 8  |

| SG1 Measurement Registers                                      | 8  |

| Vout/Vexc                                                      | 8  |

| Strain                                                         | 8  |

| Minimum Strain                                                 | 8  |

| Maximum Strain                                                 | 8  |

| SG1 Control Registers                                          | 9  |

| Bridge Configuration Type                                      | 9  |

| PGA                                                            | 10 |

| Sample Rate                                                    | 11 |

| Nominal Strain Gauge Resistance                                | 11 |

| Gauge Factor                                                   | 11 |

| Poisson Ratio                                                  | 12 |

| Lead Resistance                                                | 12 |

| Excitation Voltage                                             | 12 |

| Wire Select Mode                                               | 12 |

| Reset Minimum and Maximum Strain                               | 13 |

| Use Internal Bridge Completion                                 | 13 |

| Strain Alert Detect Programming                                | 14 |

| Strain Alert Detect 1                                          | 14 |

| Strain Alert Detect 2                                          | 14 |

| Status and Interrupt Registers                                 | 15 |

| BIT Loop Status                                                | 15 |

| BIT Amp Status                                                 | 15 |

| BIT Status                                                     | 16 |

| Strain Alert Status                                            | 16 |

| Error Summary Status                                           | 17 |

| Interrupt Vector and Steering                                  | 18 |

| FUNCTIONAL REGISTER MAP                                        | 19 |

| SG1 Measurement Registers                                      | 19 |

| SG1 Control Registers                                          | 19 |

| Strain Alert Detect Programming Registers                      | 20 |

| Status Registers                                               | 21 |

| BIT Registers                                                  | 21 |

| Status Registers                                               | 21 |

| Interrupt Registers                                            | 22 |

| APPENDIX: PIN-OUT DETAILS                                      | 24 |

| MODULE MANUAL - STATUS AND INTERRUPTS                          | 25 |

| STATUS AND INTERRUPTS                                          | 26 |

| Interrupt Vector and Steering                                  | 26 |

| Interrupt Trigger Types                                        | 27 |

| Dynamic and Latched Status Registers Examples                  | 28 |

| Interrupt Examples                                             | 29 |

| NAI Cares               | 31 |

|-------------------------|----|

| FAQ                     | 31 |

| Application Notes       | 31 |

| Calibration and Repairs | 31 |

| Call Us                 | 31 |

|                         |    |

### **Revision History**

| Module Ma | Module Manual - SG1 Revision History |                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|-----------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Revision  | Revision<br>Date                     | Description                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

| с         | 2022-10-<br>11                       | EC0 C09714, transition to docbuilder format. Pg.5 thru 7, changed "Delta-Sigma" to "Sigma-Delta". Pg.6, remove FIR filter mode reference from Output Data Rate. Pg.7, added Status and Interrupts paragraph. Pg.13, changed Reset Min & Max Strain from R/W to W. Added Appendix: Pin-Out Details. |  |  |  |  |  |  |  |  |  |  |

| Module Man | Module Manual - Status and Interrupts Revision History |             |  |  |  |  |  |  |  |  |  |

|------------|--------------------------------------------------------|-------------|--|--|--|--|--|--|--|--|--|

| Revision   | Revision Date                                          | Description |  |  |  |  |  |  |  |  |  |

| С          | 2021-11-30                                             |             |  |  |  |  |  |  |  |  |  |

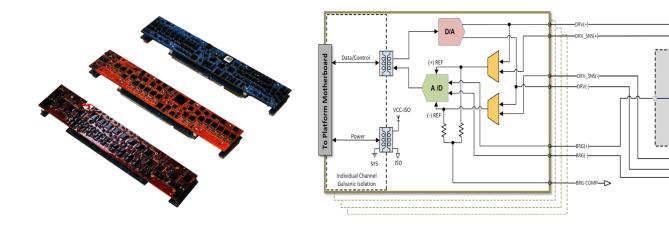

# SG1 Measurement & Simulation Modules Strain Gauge Measurement Function Modules

### 4 Channels, Strain Gauge Measurement

Module SG1 is NAI's latest generation Strain Gauge Measurement Module. This intelligent, four-channel module is used on our Multifunction Embedded I/O Boards and Single Board Computers (SBCs).

While there are several methods of measuring mechanical strain, the most common is with a strain gauge. The gauge provides electrical resistance that varies in proportion to the amount of strain in the device. The most widely used gauge is the bonded metallic strain gauge. To measure such small changes in resistance, strain gauges are almost always used in a bridge configuration with a voltage excitation source. The general Wheatstone bridge (conventional, 4-arm bridge) consists of four resistive arms with an excitation voltage, Vexc, that is applied across the bridge.

The SG1 module uses four independent, isolated input A/Ds. This module is designed to read output signals from a completed Wheatstone bridge (i.e., it can be used with one or more strain gauge elements as a completed 4-arm Wheatstone bridge) and is commonly used in applications requiring pressure, weight, and stress transducers interface/measurement. Each channel incorporates an  $\Sigma$ - $\Delta$  modulator, a PGA, and on-chip digital filtering intended for the measurement of wide dynamic range signals. Each channel also contains a fourth order digital filter, with several programmable filter options. When properly applied, the filter has deep notches at either 50 or 60 Hz.

The SG1 module provides a DC excitation, programmable from 2 - 12 VDC for interfacing to most load and accelerometer gauges.

The on-board processor/FPGA resources remove the user from the details of managing the A/D interface, register access, and sample timing. The processor firmware provides the user with a simpler user interface with high-level commands and post-calibration data. The module also contains internal factory calibration values stored in Flash. The SG1 automatically recalibrates for changes in reference voltage and die temperature.

Both internal and system calibration are included, providing the user with the option of removing only offset/gain errors internal to the A/Ds or the offset/gain errors of the complete end system.

#### **Features**

- Four independent, isolated input A/Ds

- Designed to read output signals from a completed Wheatstone bridge

Used in applications requiring pressure, weight, and stress transducers

- interface and measurement

- On-chip digital filtering for wide dynamic range signal measurement

- DC excitation for load and accelerometer gauge interface (programmable from 2-12 VDC)

- Onboard management of:

- AD interface

- Register access

Sample timing

- Internal and system calibration is included

#### **Specifications**

North Atlantic

Industries

| -                                |                                                                                                                                                                                                                   |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of Channels               | 4 differential input channels for load cell & accelerometer measurement.                                                                                                                                          |

| Input Interface                  | Conventional 4-arm Wheatstone bridge, 4 or 6-wire interface.                                                                                                                                                      |

| A/D Converter                    | 32-bit Sigma-Delta                                                                                                                                                                                                |

| Output Resolution                | 32-bit                                                                                                                                                                                                            |

| Accuracy                         | ± 0.1% Full-Scale (FS) range                                                                                                                                                                                      |

| Digital Output                   | Percent of Full Scale; Ratio (Vin/Vexc)                                                                                                                                                                           |

| Gain Settings                    | 1, 2, 4, 8, 16, and 32 (programmable)                                                                                                                                                                             |

| Input Impedance                  | > 10 ΜΩ                                                                                                                                                                                                           |

| Input Coupling                   | DC                                                                                                                                                                                                                |

| Bridge Excitation Voltage (Vexc) | Independent Sources, Programmable 2 - 12 VDC                                                                                                                                                                      |

| Output Current (Maximum)         | 100 mA / source                                                                                                                                                                                                   |

| Remote Voltage Sensing           | Yes                                                                                                                                                                                                               |

| Output Data Rate                 | 2.5 to 38,400 Hz (dependent on programmable filter settings).                                                                                                                                                     |

| BIT (Built-in-Test)              | Continuous background "online" accuracy, open detection capability.                                                                                                                                               |

| ESD Protection                   | Designed to meet the testing requirements of IEC 801-2 Level 2. (4 kV transient with a peak current of 7.5 A and a time constant of approximately 60 ns)                                                          |

| Enhanced Functionality (pending) | Each channel provided with: Programmable FFT with selectable sample rate and number of points (up to 64K). User selectable windowing function. Store value of unstrained voltage to include as compensation value |

| Power                            | 5 VDC @ 850 mA typical (est.)                                                                                                                                                                                     |

| Ground                           | Channels isolated from each other and system ground.                                                                                                                                                              |

| Weight                           | 1.5 oz. (42 g)                                                                                                                                                                                                    |

#### Architected for Versatility

NAI's Configurable Open Systems Architecture<sup>™</sup> (COSA®) offers a choice of over 100 smart I/O, communications, or Ethernet switch functions, providing the highest packaging density and greatest flexibility of ruggedized embedded product solutions in the industry. Preexisting, fully-tested functions can be combined in an unlimited number of ways quickly and easily.

#### **One-Source Efficiencies**

Eliminate man-months of integration with a configured, field-proven system from NAI. Specification to deployment is a seamless experience as all design, state-of-the-art manufacturing, assembly and test are performed - by one trusted source. All facilities are located within the U.S. and optimized for high-mix/low volume production runs and extended lifecycle support.

#### **Product Lifecycle Management**

From design to production and beyond, NAI's product lifecycle management strategy ensures the long-term availability of COTS products through configuration management, technology refresh and obsolescence component purchase and storage.

All specifications are subject to change without notice. All product and company names are trademarks or registered trademarks of their respective holders

#### INTRODUCTION

This module manual provides information about the North Atlantic Industries, Inc. (NAI) Strain Gauge (SG) Measurement Function Module: SG1. This module is compatible with all latest generation NAI motherboards.

The <u>SG1</u> provides four differential input channels for load cell & accelerometer measurement.

#### **FEATURES**

- Four independent, isolated input A/Ds

- Designed to read output signals from a completed Wheatstone bridge

- · Used in applications requiring pressure, weight and stress transducers interface/measurement.

- · On-chip digital filtering for wide dynamic range signal measurement

- DC excitation for load and accelerometer gauge interface (programmable from 2-12 VDC)

- Onboard management of A/D interface, register access and sample timing

- · Internal and system calibration included

#### **PRINCIPLE OF OPERATION**

The SG1 module is NAI's latest generation Strain Gauge Measurement Module. This intelligent, four-channel module is used on our multifunction embedded boards and SBCs to provide load cell and accelerometer element measurement interfaces.

While there are several methods of measuring mechanical strain, the most common is with a strain gauge. The gauge provides electrical resistance that varies in proportion to the amount of strain in the device. The most widely used gauge is the bonded metallic strain gauge. To measure such small changes in resistance, strain gauges are almost always used in a bridge configuration with a voltage excitation source. The general Wheatstone bridge (conventional, 4-arm bridge) consists of four resistive arms with an excitation voltage, Vexc, that is applied across the bridge.

The SG1 module uses four independent, isolated input A/Ds. This module is designed to read output signals from a completed Wheatstone bridge (i.e., it can be used with one or more strain gauge elements as a completed 4-arm Wheatstone bridge) and is commonly used in applications requiring pressure, weight, and stress transducers interface/measurement. Each channel incorporates a  $\Sigma$ - $\Delta$  (Sigma-Delta) modulator, a PGA, and on-chip digital filtering intended for the measurement of wide dynamic range signals. Each channel also contains a fourth order digital filter, with several programmable filter options. When properly applied, the filter has deep notches at either 50 or 60 Hz.

The SG1 module provides a DC excitation, programmable from 2 – 12 VDC for interfacing to most load and accelerometer gauges.

The on-board processor/FPGA resources remove the user from the details of managing the A/D interface, register access, and sample timing. The processor firmware provides the user with a simpler user interface with high-level commands and post-calibration data. The module also contains internal factory calibration values stored in Flash.

#### Automatic Background Built-in Test (BIT)/Diagnostic Capability

Automatic background BIT testing is provided. Each channel is checked at periodic intervals for correct A/D operation. Any failure triggers an interrupt if enabled, with the results available in the status registers. The testing is transparent to the user and has no effect on the operation of this module.

#### **Status and Interrupts**

The SG Strain Gauge Measurement Module provide registers that indicate faults or events. Refer to "Status and Interrupts Module Manual" for the Principle of Operation description.

#### **REGISTER DESCRIPTIONS**

The register descriptions provide the Register Name, Type, Data Range, Read or Write information, power on default initialized values, a description of the function and a data table where applicable.

#### **SG1 Measurement Registers**

The SG1 measurement registers provide Vout/Vexc ratio measurements, strain measurements, and minimum/maximum strain readings.

#### Vout/Vexc

Function: Measures the ratio of the bridge output voltage to the excitation voltage.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: -1.0 to +1.0

Read/Write: R

#### Initialized Value: N/A

**Operational Settings:** Vout/Vexc measurement in V/V.

|     | Vout/Vexc |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30       | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| D   | D         | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

| D15 | D14       | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| D   | D         | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

#### Strain

Function: Measures the level of mechanical strain.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: -1000.0 to 1000.0

Read/Write: R

Initialized Value: N/A

**Operational Settings:** Strain is calculated based on the Vout/Vexc reading, bridge configuration type, nominal strain gauge resistance, gauge factor, Poisson ratio, and lead resistance. Units are in micro-strain (με).

#### Minimum Strain

Function: Stores the minimum strain level. When a new strain reading is lower than the value in this register, it will replace it.

**Type:** Single Precision Floating Point Value (IEEE-754)

Data Range: -1000.0 to 1000.0

Read/Write: R

Initialized Value: N/A

**Operational Settings:** Reset this value to zero by writing to the min/max reset register.

#### Maximum Strain

Function: Stores the maximum strain level. When a new strain reading is higher than the value in this register, it will replace it.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: -1000.0 to 1000.0

Read/Write: R

Initialized Value: N/A

Operational Settings: Reset this value to zero by writing to the min/max reset register.

#### **SG1** Control Registers

The SG1 control registers provide the ability to configure the channels for the strain gauge interface and application.

#### Bridge Configuration Type

Function: Selects the bridge and strain gauge configuration.

Type: unsigned binary word (32-bit)

Data Range: 0x0 to 0x6

Read/Write: R/W

Initialized Value: 0x0 (Quarter Bridge 1)

Operational Settings: See below table for compatible configurations.

| Configuration<br>Types | Register<br>Value | Configuration Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Strain Formula                                                                                                  |

|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Quarter-Bridge I       | 0x0               | $V_{\mathrm{in}} \overset{R_{\mathrm{i}}}{\underbrace{\qquad}} \overset{R_{\mathrm{i}}}{\underbrace{}} \overset{R_{\mathrm{i}}}{\underbrace{}} \overset{R_{\mathrm{i}}}{\underbrace{}} \overset{R_{\mathrm{i}}}{\underbrace{}} \overset{R_{\mathrm{i}}}{\underbrace{\atop}} \overset{R_{\mathrm{i}}}{\underbrace{I}} \overset{R_{\mathrm{i}}}{\underbrace{I}} \overset{R_{\mathrm{i}}}{\underbrace{I}} \overset{R_{\mathrm{i}}}{$ | Strain (c) = $\frac{-4V_r}{GF(1+2V_r)} \bullet \begin{bmatrix} 1 + \frac{R_L}{R_G} \end{bmatrix}$               |

| Quarter-Bridge II      | 0x1               | $\mathbf{V}_{u} \begin{pmatrix} \bullet \\ \mathbf{R}_{i}^{T_{i}} & \bullet \\ \mathbf{R}_{i}^{T_{i}} & \mathbf{R}_{i} \\ \\ \mathbf{R}_{i} \\ \mathbf{R}_{i}^{T_{i}} & \mathbf{R}_{i} \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Strain ( $\varepsilon$ ) = $\frac{-4V_r}{GF(1+2V_r)}  \bullet  \left[ 1 + \frac{R_L}{R_G} \right]$              |

| Half-Bridge I          | 0x2               | $V_{\mathrm{s}} \overset{P_{i}}{} \overset{P_{i}}{\underset{R_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P_{i}}{\overset{P}}{\overset{P}}{\overset{P_{i}}{\overset{P}}{\overset{P}}{\overset{P}{\overset{P}}}{\overset{P_{i}}{\overset{P}}{\overset{P}}{\overset{P}}{\overset{P}}{\overset{P}}{\overset{P}}{\overset{P}}{\overset{P}}}}}}}}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Strain ( $\varepsilon$ ) = $\frac{-4V_{r}}{GF[(1+v)-2V_{r}(v-1)]} \bullet \left[1 + \frac{R_{L}}{R_{G}}\right]$ |

| Half-Bridge II         | 0x3               | $R_{i}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Strain ( $\varepsilon$ ) = $\frac{-2V_{f}}{GF} \cdot \left[ 1 + \frac{R_{L}}{R_{G}} \right]$                    |

| Full-Bridge I          | 0x4               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Strain (ε) =V <sub>r</sub><br>                                                                                  |

| Full-Bridge II         | 0x5               | Va (* )<br>Va (*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Strain (ε) = -2V <sub>r</sub><br>GF (ν+1)                                                                       |

| Full-Bridge III        | 0x6               | $V_{c}$ $+$ $+$ $+$ $+$ $+$ $+$ $+$ $+$ $+$ $+$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Strain (ε) =<br><u>-2V<sub>r</sub></u><br>GF [( v + 1) - V <sub>r</sub> (v-1)]                                  |

#### PGA

Function: Sets the gain of the A/D.

Type: unsigned binary word (32-bit)

Data Range: 0x0 to 0x5 (See table)

Read/Write: R/W

Initialized Value: 0x2 (4V/V)

**Operational Settings:** Set the value based on the PGA table

| PGA<br>Register Value | Gain<br>(V/V) |

|-----------------------|---------------|

| 0x0                   | 1             |

| 0x1                   | 2             |

| 0x2                   | 4             |

| 0x3                   | 8             |

| 0x4                   | 16            |

| 0x5                   | 32            |

|     | PGA |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30 | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | D   | D   | D   |

#### Sample Rate

**Function:** Sets the sampling rate of the A/D.

Type: unsigned binary word (32-bit)

Data Range: 0x0 to 0xF (See table)

Read/Write: R/W

Initialized Value: 0x0 (2.5 SPS)

**Operational Settings:** Set the value based on Sample Rate table. Note: lower rates provide greater stability and accuracy in the readings. Per channel configuration.

| Sample Rate<br>Register Value | Sample Rate<br>(SPS) | Bandwidth<br>(Hz) |

|-------------------------------|----------------------|-------------------|

| 0x0                           | 2.5                  | 1.25              |

| 0x1                           | 5                    | 2.5               |

| 0x2                           | 10                   | 5                 |

| 0x3                           | 16.6666              | 8.3333            |

| 0x4                           | 20                   | 10                |

| 0x5                           | 50                   | 25                |

| 0x6                           | 60                   | 30                |

| 0x7                           | 100                  | 50                |

| 0x8                           | 400                  | 200               |

| 0x9                           | 1200                 | 600               |

| 0xA                           | 2400                 | 1200              |

| 0xB                           | 4800                 | 2400              |

| 0xC                           | 7200                 | 3600              |

| 0xD                           | 14400                | 7200              |

| 0xE                           | 19200                | 9600              |

| 0xF                           | 38400                | 19200             |

|     | Sample Rate |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30         | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14         | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | D   | D   | D   | D   |

#### Nominal Strain Gauge Resistance

Function: User defined resistance of the strain gauge in an unstrained condition.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: N/A

Read/Write: R/W

**Initialized Value:** 350.0 (programmed in ohms)

Operational Settings: Sets the user defined nominal strain gauge resistance to be used for strain calculation.

#### Gauge Factor

Function: User defined ratio of the fractional change in resistance to the fractional change in strain.

**Type:** Single Precision Floating Point Value (IEEE-754)

Data Range: N/A

Read/Write: R/W

Initialized Value: 2.0

Operational Settings: Sets the user defined gauge factor to be used for strain calculation.

#### Poisson Ratio

Function: User defined negative ratio of the strain in the transverse direction to the strain in the axial direction.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: N/A

Read/Write: R/W

Initialized Value: 0.3

Operational Settings: Sets the user defined Poisson ratio to be used for strain calculation.

#### Lead Resistance

Function: User defined resistance of the wires connecting the bridge to the module.

**Type:** Single Precision Floating Point Value (IEEE-754)

Data Range: N/A

Read/Write: R/W

**Initialized Value:** 0.0 (programmed in ohms)

Operational Settings: Sets the user defined lead resistance to be used for strain calculation.

#### Excitation Voltage

Function: User defined bridge excitation voltage.

Type: unsigned binary word (32-bit)

Data Range: 0x0 to 0xFFF (0.0V to 12V)

Read/Write: R/W

Initialized Value: 0x0 (off)

**Operational Settings:** Programmable bridge excitation voltage up to 12V. 12-bit value, LSB is calculated by 12V / (2<sup>12</sup>-1) and is approximately 2.93mV.

|     | Excitation Voltage |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|--------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30                | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0                  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14                | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0                  | 0   | 0   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

#### Wire Select Mode

**Function:** Selects where to sense the excitation voltage. A 6-wire connection is required to sense the excitation voltage at the bridge. If the voltage sensing is done internally, only 4 wires are required.

Type: unsigned binary word (32-bit)

Data Range: 0x4, 0x6

Read/Write: R/W

Initialized Value: 0x4 (internal sensing)

Operational Settings: Set the Wire Measurement Mode as specified in the table.

| Wire Select Mode<br>Value | Description                            |

|---------------------------|----------------------------------------|

| 0x4                       | 4-wire configuration, internal sensing |

| 0x6                       | 6-wire configuration, remote sensing   |

|     | Wire Select Mode |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30              | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14              | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | D   | D   | D   |

#### Reset Minimum and Maximum Strain

Function: Resets the channel's minimum and maximum strain readings.

Type: unsigned binary word (32-bit)

Data Range: 0x0 to 0xF

Read/Write: W

Initialized Value: 0x0

Operational Settings: Writing a '1' resets the channel's minimum and maximum strain readings to 0.0. Bit-mapped by channel.

|     | Reset Minimum and Maximum Strain |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|----------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30                              | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0                                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14                              | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0                                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | D   | D   | D   | D   |

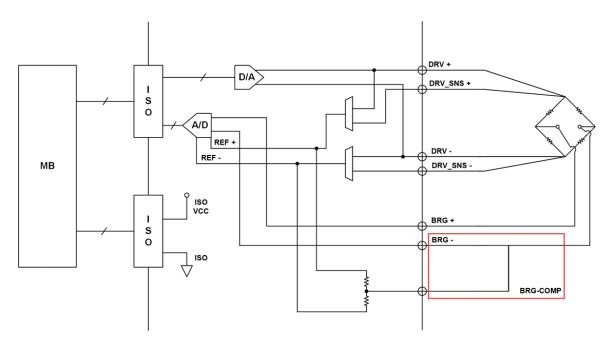

#### Use Internal Bridge Completion

**Function:** Enables the bridge completion circuitry. When enabled, the user needs only to connect a half-bridge, and connect the bridge completion pin to the sense low pin.

Type: unsigned binary word (32-bit)

Data Range: 0x0 to 0xF

Read/Write: R/W

Initialized Value: 0x0

**Operational Settings:** If configured with two arms of the Wheatstone bridge external to the module, the user must complete the bridge using the module's internal half-bridge. This is accomplished by wiring the BRG-COMP pin to the BRG - pin (as shown below).

Writing a '1' enables the bridge completion circuit for the channel. Bit-mapped per channel.

|     | Use Internal Bridge Completion |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|--------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30                            | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0                              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14                            | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0                              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | D   | D   | D   | D   |

#### Strain Alert Detect Programming

The SG1 Strain Alert registers provide the ability to program four strain thresholds that will result in strain alerts.

#### Strain Alert Detect 1

A "low" and a "high" threshold value is specified for each strain threshold that will be used to set the Strain Alert statuses. The Low Strain Alert 1 register sets the threshold value to use to set the Low Strain Alert 1 status bit when the Strain reading is less than or equal to the low strain threshold value. Conversely, the High Strain Alert 1 register sets the threshold values to use to set the High Strain Alert 1 status bit when the Strain reading is greater than or equal to the high strain threshold value. These threshold values are individually configurable on a per channel basis.

Low Strain Alert 1

Function: Sets Low Strain Alert 1 value in micro-strain (µɛ) for each channel.

**Type:** Single Precision Floating Point Value (IEEE-754)

Data Range: -1000.0 to 1000.0

Read/Write: R/W

Initialized Value: 0.0

**Operational Settings:** If the measured strain is less than or equal to the set value, then a *Low Strain Alert 1 Status* will be set. An interrupt will occur if the *Low Strain Alert 1 Interrupt Enable* register is set to **1**.

#### High Strain Alert 1

Function: Sets High Strain Alert 1 value in micro-strain ( $\mu\epsilon$ ) for each channel.

**Type:** Single Precision Floating Point Value (IEEE-754)

Data Range: -1000.0 to 1000.0

Read/Write: R/W

#### Initialized Value: 0.0

**Operational Settings:** If the measured strain is greater than or equal to the set value, then a *High Strain Alert 1 Status* will be set. An interrupt will occur if the *High Strain Alert 1 Interrupt Enable* register is set to **1**.

#### Strain Alert Detect 2

A "low" and a "high" threshold value is specified for each strain threshold that will be used to set the Strain Alert statuses. The *Low Strain Alert 2* register sets the threshold value to use to set the *Low Strain Alert 2* status bit when the Strain reading is less than or equal to the low strain threshold value. Conversely, the *High Strain Alert 2* register sets the threshold values to use to set the *High Strain Alert 2* status bit when the Strain reading is greater than or equal to the high strain threshold value. These threshold values are individually configurable on a per channel basis.

#### Low Strain Alert 2

Function: Sets Low Strain Alert 2 value in micro-strain ( $\mu\epsilon$ ) for each channel.

Type: Single Precision Floating Point Value (IEEE-754)

Data Range: -1000.0 to 1000.0

Read/Write: R/W

#### Initialized Value: 0.0

**Operational Settings:** If the measured strain is less than or equal to the set value, then a *Low Strain Alert 2 Status* will be set. An interrupt will occur if the *Low Strain Alert 2 Interrupt Enable* register is set to **1**.

#### High Strain Alert 2

Function: Sets High Strain Alert 2 value in micro-strain ( $\mu\epsilon$ ) for each channel.

**Type:** Single Precision Floating Point Value (IEEE-754)

Data Range: -1000.0 to 1000.0

Read/Write: R/W

Initialized Value: 0.0

**Operational Settings:** If the measured strain is greater than or equal to the set value, then a *High Strain Alert 2 Status* will be set. An interrupt will occur if the *High Strain Alert 2 Interrupt Enable* register is set to **1**.

#### **Status and Interrupt Registers**

The SG1 Module provides status registers for BIT, and Strain Alert.

#### BIT Loop Status

Function: This test represents the dynamic status of the BIT Loop test that checks the A/D interface and A/D operation health

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0x0000 000F

Read/Write: R

Initialized Value: 0

Operational Settings: The logic OR of this status along with the BIT Amp Status makes up the overall BIT status.

|     | BIT Loop Status |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30             | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14             | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Ch4 | Ch3 | Ch2 | Ch1 |

#### BIT Amp Status

Function: This test represents the dynamic status of the BIT Amp test that checks the front-end circuitry of the channel

**Type:** unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0x0000 000F

Read/Write: R

#### Initialized Value: 0

Operational Settings: The logic OR of this status along with the BIT Loop Status makes up the overall BIT status

|     | BIT Amp Status |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D31 | D30            | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14            | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Ch4 | Ch3 | Ch2 | Ch1 |

#### BIT Status

There are four registers associated with the BIT Status: Dynamic, Latched, Interrupt Enable, and Set Edge/Level Interrupt.

|     | BIT Dynamic Status           |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|     | BIT Latched Status           |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|     | BIT Interrupt Enable         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|     | BIT Set Edge/Level Interrupt |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| D31 | D30                          | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| 0   | 0                            | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| D15 | D14                          | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| 0   | 0                            | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Ch4 | Ch3 | Ch2 | Ch1 |

Function: Indicates the corresponding channel BIT status or configuration

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0x0000 000F

Read/Write: R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt)

Initialized Value: 0

#### Strain Alert Status

There are four registers associated with each of the Strain Alert Statuses: Dynamic, Latched, Interrupt Enable, and Set Edge/Level Interrupt.

|                                              | Strain Alert Low 1 Dynamic Status |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

|----------------------------------------------|-----------------------------------|-----|-----|-----|--------|-----------|-----------|-----------|-----------|---------|-----|-----|-----|-----|-----|

| Strain Alert Low 1 Dynamic Status            |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

|                                              |                                   |     |     |     | St     | train Ale | ert Low   | 1 Latch   | ed Statu  | IS      |     |     |     |     |     |

|                                              |                                   |     |     |     | St     | rain Ale  | rt Low 1  | l Interru | ipt Enab  | le      |     |     |     |     |     |

|                                              |                                   |     |     |     | Strain | Alert Lo  | ow 1 Set  | t Edge/L  | evel Int  | errupt  |     |     |     |     |     |

|                                              |                                   |     |     |     | St     | rain Ale  | rt High   | 1 Dynar   | nic Stat  | us      |     |     |     |     |     |

| Strain Alert High 1 Latched Status           |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

| Strain Alert High 1 Interrupt Enable         |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

| Strain Alert High 1 Set Edge/Level Interrupt |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

| Strain Alert Low 2 Dynamic Status            |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

| Strain Alert Low 2 Dynamic status            |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

| Strain Alert Low 2 Interrupt Enable          |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

| Strain Alert Low 2 Set Edge/Level Interrupt  |                                   |     |     |     |        |           |           |           |           |         |     |     |     |     |     |

|                                              |                                   |     |     |     | St     | rain Ale  | rt High : | 2 Dynar   | nic Stat  | us      |     |     |     |     |     |

|                                              |                                   |     |     |     | St     | rain Ale  | ert High  | 2 Latch   | ed Statı  | IS      |     |     |     |     |     |

|                                              |                                   |     |     |     | St     | rain Ale  | rt High 2 | 2 Interru | upt Enab  | ole     |     |     |     |     |     |

|                                              |                                   |     |     |     | Strain | Alert Hi  | gh 2 Se   | t Edge/l  | Level Int | terrupt |     |     |     |     |     |

| D31                                          | D30                               | D29 | D28 | D27 | D26    | D25       | D24       | D23       | D22       | D21     | D20 | D19 | D18 | D17 | D16 |

| 0                                            | 0                                 | 0   | 0   | 0   | 0      | 0         | 0         | 0         | 0         | 0       | 0   | 0   | 0   | 0   | 0   |

| D15                                          | D14                               | D13 | D12 | D11 | D10    | D9        | D8        | D7        | D6        | D5      | D4  | D3  | D2  | D1  | D0  |

| 0                                            | 0                                 | 0   | 0   | 0   | 0      | 0         | 0         | 0         | 0         | 0       | 0   | Ch4 | Ch3 | Ch2 | Ch1 |

Function: Sets the corresponding bit associated with the channel's Strain Alert indication for strain readings that are below or above the associated thresholds.

**Type:** unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0x0000 000F

Read/Write: R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt)

Initialized Value: 0

#### Error Summary Status

There are four registers associated with the Summary Status: Dynamic, Latched, Interrupt Enable, and Set Edge/Level Interrupt.

|     | Summary Status Dynamic Status           |     |     |     |     |    |    |    |    |    |    |     |     |     |     |

|-----|-----------------------------------------|-----|-----|-----|-----|----|----|----|----|----|----|-----|-----|-----|-----|

|     | Summary Status Latched Status           |     |     |     |     |    |    |    |    |    |    |     |     |     |     |

|     | Summary Status Interrupt Enable         |     |     |     |     |    |    |    |    |    |    |     |     |     |     |

|     | Summary Status Set Edge/Level Interrupt |     |     |     |     |    |    |    |    |    |    |     |     |     |     |

| D31 |                                         |     |     |     |     |    |    |    |    |    |    |     |     |     |     |

| 0   | 0                                       | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   |

| D15 | D14                                     | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3  | D2  | D1  | D0  |

| 0   | 0                                       | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | Ch4 | Ch3 | Ch2 | Ch1 |

Function: Sets the corresponding bit when a fault is detected for BIT on that channel.

Type: unsigned binary word (32-bit)

Data Range: 0x0000 0000 to 0x0000 000F

Read/Write: R (Dynamic), R/W (Latched, Interrupt Enable, Edge/Level Interrupt)

Initialized Value: 0

#### Summary Events Table

| Module | BIT | Overcurrent | External<br>Power<br>Loss | <br>External<br>Power Under<br>Volt | External<br>Power Over<br>Volt | Over<br>Temp | Surge<br>Suppressor<br>Fault |

|--------|-----|-------------|---------------------------|-------------------------------------|--------------------------------|--------------|------------------------------|

| SG1    | Х   |             |                           |                                     |                                |              |                              |

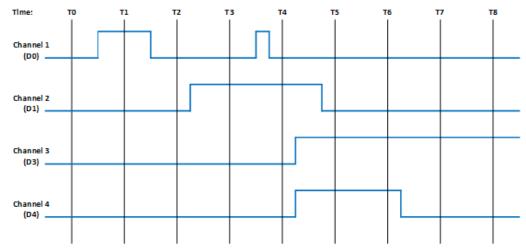

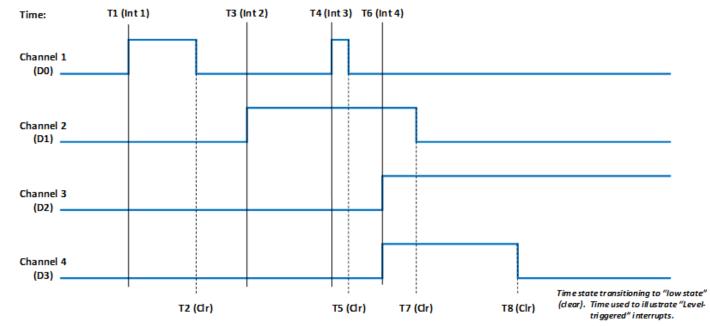

#### Interrupt Vector and Steering